ELSEVIER

Contents lists available at ScienceDirect

# Journal of Alloys and Compounds

journal homepage: www.elsevier.com/locate/jallcom

# A comparative study on the electrical characteristics of Au/n-Si structures with anatase and rutile phase TiO<sub>2</sub> interfacial insulator layer

A. Bengi\*, U. Aydemir, Ş. Altındal, Y. Özen, S. Özçelik

Department of Physics, Faculty of Arts and Sciences, Gazi University, 06500, Ankara, Turkey

#### ARTICLE INFO

## Article history: Received 2 March 2010 Received in revised form 15 June 2010 Accepted 15 June 2010 Available online 25 June 2010

Keywords: TiO<sub>2</sub> DC magnetron sputtering Electrical characterization Interface state density Series resistance

#### ABSTRACT

TiO<sub>2</sub> thin films were deposited on polycrystalline n-type Si substrate using DC magnetron sputtering system. To improve the crystal quality, thermal annealing (TA) process was done at 700 °C and 900 °C. The effect of TA on the structural properties was investigated using high resolution X-ray diffraction (HRXRD). It was observed that the phase transition from amorphous phase to anatase and rutile phases occurs at 700 °C and 900 °C, respectively. Au/TiO<sub>2</sub>/n-Si structures were also fabricated for the investigation of TA on the main electrical parameters, such as ideality factor (n), barrier height  $(\Phi_B)$ , series resistance  $(R_s)$ , shunt resistance  $(R_{sh})$  and interface states  $(N_{ss})$ . The current-voltage (I-V) and capacitance-voltage (C-V) characteristics have been investigated at room temperature and results have been compared with each other. The electrical characteristics showed that TA strongly affects the main electrical parameters. The rectifying ratio of Au/n-Si structures with anatase phase TiO<sub>2</sub> was to be 140 while the rutile phase was to be 8864. The leakage current was also found to be very sensitive to the annealing temperature, and also the magnitude of the leakage current for rutile phase is 15 times lower than the anatase phase's. In addition, the energy distribution profile of N<sub>ss</sub> of the structures was obtained from the forward bias I-V data by taking the bias dependence of the effective barrier height ( $\Phi_{\rm e}$ ) into account. For both of the samples, the value of  $N_{ss}$  decreases with TA. Similarly, the values of  $R_{s}$  and  $R_{sh}$  of the structures obtained from the forward bias I-V data were found as  $209\,\Omega$  and  $42\,k\Omega$  for the anatase and  $59\,\Omega$  and  $598\,k\Omega$  for the rutile phase. These results show that the performance of the Au/TiO<sub>2</sub>/n-Si structure improved with thermal annealing.

© 2010 Elsevier B.V. All rights reserved.

# 1. Introduction

Alternative high-k materials such as Si<sub>3</sub>N<sub>4</sub>, HfO<sub>2</sub>, ZnO, ZrO<sub>2</sub> TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> for SiO<sub>2</sub> have recently attracted great attention for its application as an interfacial insulator layer at metal/semiconductor (M/S) interface in the semiconductor devices such as metalinsulator/oxide-semiconductor (MIS or MOS) [1-13]. SiO<sub>2</sub> has a poor interface due to high leakage current, high temperature dispersion and high defect trapped charges. Therefore, the fundamental requirement is using high k-dielectrics materials. In addition to high dielectric constant and band offers, low density of interface states and low leakage current [6-13]. Among these high-k materials, bulk TiO<sub>2</sub> is a potential candidate because of having different phases with extraordinarily high dielectric constant. There are three types of bulk crystal structure in  $TiO_2$ : (1) anatase, (2) rutile and (3) brookite type with 3.20 eV, 3.02 eV and 2.96 eV energy band gaps, respectively. Among them the brookite phase is an unstable rhombic structure. The most common phases are anatase and rutile phases whose dielectric constants are 48 and 89, respectively [1]. The anatase phase is normally formed around 600 °C, while transformation to rutile phase occurs around 800 °C [1,14–17]. In addition, the anatase phase has an indirect band gap, whereas the rutile phase has a direct band gap [15,16]. The rutile phase in particular has its potential applications in catalysis, electrochromism, high-speed memory devices, paints etc. [3,4].

There are lots of  $TiO_2$  thin film growth techniques such as chemical vapor deposition [18], electron beam evaporation [19], thermal or anodic oxidation [8,20], sol–gel method [21,22], plasma-enhanced chemical vapor deposition [23], and DC reactive magnetron sputtering methods [24,25]. Among these methods, DC reactive magnetron sputtering method is much more preferable since it is easier to control and this method makes the fabrication of insulator films with reproducible and desired properties possible. The performance and reliability of  $TiO_2$  based devices particularly depends on the formation of  $TiO_2$  layer at M/S interface, annealing temperature, density of interface states ( $N_{\rm SS}$ ) at  $Si/TiO_2$  interface, series resistance ( $R_{\rm S}$ ) of devices, and inhomogeneities of the Schottky barrier formation at M/S interface [18–22]. Kadoshima et al. [26] showed that the  $SiO_2$  formation is inevitable during thermal annealing of  $TiO_2$  and it decreases leakage current. Also, Lee et al.

<sup>\*</sup> Corresponding author. E-mail address: aylinbengi@gmail.com (A. Bengi).

[17] suggested that the decrease of leakage current was related to the growth of interfacial layer and the reduction of oxygen vacancy.

In general, the forward bias I-V characteristics of MIS structure are linear on a semi-logarithmic scale at intermediate bias voltage but deviate considerably from linearity due to the effect of  $R_{\rm S}$  and  $N_{\rm SS}$  when the applied voltage is sufficiently large ( $V \ge 1$  V). Usually, interface states can be divided into two groups in the view of interfacial insulator layer thickness ( $\delta$ ). One of these groups ( $\delta \le 30$  Å) communicates most rapidly with the metal, while the other group ( $\delta \ge 30$  Å) communicates most rapidly with the semiconductor [27,28]. The relation among the semiconductor and the value of ideality factor (n), increases as the insulator layer thickness increases. The values of  $R_{\rm S}$  and  $N_{\rm SS}$  can also affect the C-V characteristics of devices, by causing a bending of C-V plots in the accumulation region.

In this study, the main electrical parameters of  $Au/TiO_2/n-Si$  structures with anatase and rutile phase  $TiO_2$  interfacial insulator layer such as ideality factor, leakage current, barrier height, series resistance, shunt resistance and density of interface states have been investigated at room temperature using forward and reverse bias I-V and C-V measurements. The purpose of this study is to make a comparison of the main electrical parameters of Au/n-Si structures with anatase and rutile phase  $TiO_2$  thin films in terms of  $N_{SS}$  and  $R_S$  to determine the most suitable one for device applications. In addition, the energy distribution profile of  $N_{SS}$  of the  $Au/TiO_2/n-Si$  (MIS) structures were obtained from the forward bias I-V characteristics by taking both the bias dependence of the effective barrier height and  $R_S$  for these kind of films into account and the obtained results were compared with each other.

#### 2. Experimental details

Au/TiO<sub>2</sub>/n-Si structures were fabricated on a 2" diameter with (100) orientation, 350  $\mu$ m thickness. 0.01  $\Omega$  cm resistivity and phosphorus doped (n-type) polycrystalline Si substrate. TiO2 thin films with 1500 Å thickness were deposited on n-Si substrate using DC magnetron sputtering system. Prior to the deposition of the TiO<sub>2</sub> thin film, the Si substrate was cleaned using CHClCCl<sub>2</sub>, CH<sub>3</sub>COCH<sub>3</sub>, and CH<sub>3</sub>OH organic solvents, respectively. After the cleaning step, the Si substrate was etched in a sequence of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> 20% HF, a solution of 6HNO<sub>3</sub>:1HF:35H<sub>2</sub>O, 20% HF and finally rinsed in de-ionized water (resistivity of 18 M $\Omega$  cm). Latter to cleaning and etching steps, the Si substrate was mounted on the stainless steel optically heated sputtering holder and loaded in the DC magnetron sputtering system. Before the TiO<sub>2</sub> deposition, Si substrates were heated up to 400 °C in 10<sup>-8</sup> mbar vacuum and sputter cleaned in pure argon ambient to ensure the removal of any residual organics. After the preparation of the substrate for the deposition of TiO2 thin film, the Si substrate was transferred into the deposition chamber. TiO<sub>2</sub> thin film was deposited using high purity (99.999%) Ti target, under specific Ar+O2 reactive gas mixture  $(Ar/O_2 = 90/10 \text{ sccm})$  controlled with mass flow controllers. For the deposition, the substrate temperature and the pressure was set to 200 °C and  $4.2 \times 10^{-3}$  mbar, respectively and kept constant during the whole deposition.

The deposited  $TiO_2/n$ -Si sample was cut into three pieces and thermal annealing process in air for 4 h at 700 °C and 900 °C were held to improve the film quality. The structural changes due to temperature dependent phase transitions from amorphous phase to anatase or rutile phases were carried out using high resolution X-ray diffraction (HRXRD). According to the HRXRD measurements, the as-deposited sample shows the amorphous structure while the samples annealed at 700 °C and 900 °C shows anatase and rutile phases, respectively.

After the structural characterization, the electrical characterization was done to compare the main electrical parameters such as ideality factor, leakage current, barrier height, series resistance and density of interface states. For the electrical characterization, firstly the ohmic and rectifier contacts were formed using thermal evaporation system. The ohmic back contacts were formed by deposition of high purity Au (99.999%) at 450 °C, under  $10^{-7}$  mbar vacuum and the sample was annealed at 400 °C to achieve good ohmic contact behavior. Then, the sample was also tested to see whether or not it has a good ohmic contact behavior. After then, dot shaped rectifier front contacts with 2 mm diameter and 1000 Å thickness were formed by deposition of high purity Au (99.999%) at 70 °C. After the completion of the fabrication of Au/TiO<sub>2</sub>/n-Si structures, current–voltage (I–V) measurements were performed using Keithley 2400 source–meter and capacitance–voltage (C–V) measurements were performed using HP 4192 A LF impedance analyzer (5 Hz to 13 MHz) at 1 MHz. The whole electrical measurements were made at room temperature and performed using micro computer through an IEEE–488 AC/DC converter card.

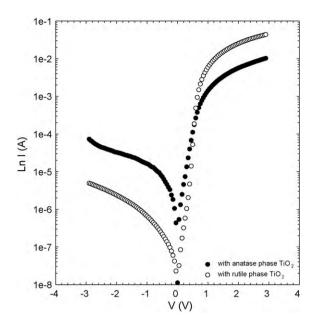

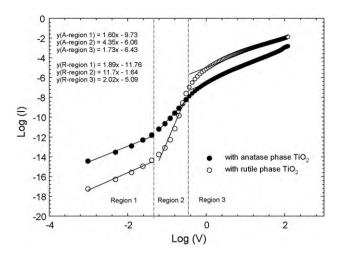

**Fig. 1.** The semi-logarithmic forward and reverse bias  $\ln I - V$  plots of the Au/n-Si structures with anatase and rutile phase  $\text{TiO}_2$  interfacial insulator layer.

# 3. Results and discussion

Fig. 1 shows the semi-logarithmic forward and reverse bias ln *I*–*V* plots of the Au/n-Si structures with anatase and rutile phase TiO<sub>2</sub> interfacial insulator layer. As can be seen from the Fig. 1, the rectifying ratio of Au/n-Si structure with anatase phase TiO<sub>2</sub> was found as 140 while the one with rutile phase was found as 8864. However, it deviates considerably from linearity at high forward bias voltages due to the effects of some factors such as series resistance  $(R_s)$ , interfacial insulator layer and interface states  $(N_{ss})$ , etc. In addition, the current rises slowly with the applied reverse bias and does not show any effect of saturation for both types of Au/n-Si structures. This non-saturating behavior of reverse current may be explained in terms of the image force lowering of Schottky barrier height [28] and the presence of the interfacial insulator layer at metal-semiconductor interface [28-43]. The leakage current was also found to be very sensitive to the annealing temperature and the magnitude of the leakage current for rutile phase is 15 times lower than the anatase phase's. These results can be attributed to the reduction of  $N_{ss}$  and  $R_{s}$  with thermal annealing in air and as a result the I-V characteristics were improved by thermal annealing

For a metal-semiconductor (MS) or metal-insulator-semiconductor (MIS) structures, the relation between current and applied forward voltage (V>3kT/q) can be expressed as [27–29],

$$I = AA^*T^2 \exp\left(-\frac{q\Phi_{\text{Bo}}}{kT}\right) \left[\exp\left(\frac{qV}{nkT}\right) - 1\right]$$

(1)

where V is the applied bias voltage, q is the electronic charge, n is the ideality factor, k is the Boltzmann constant and T is the absolute temperature in Kelvin. The reverse saturation current  $I_0$  is extracted from the straight-line intercept of  $\ln I - V$  plot at zero-bias and given by,

$$I_0 = AA^*T^2 \exp\left(-\frac{q\Phi_{\mathrm{Bo}}}{kT}\right) \tag{2}$$

where A is the rectifier contact area,  $A^*$  is the effective Richardson constant (112 A/cm<sup>2</sup> K<sup>2</sup> for n-type Si) and  $\Phi_{Bo}$  is the apparent barrier height at zero-bias, which can be obtained from Eq. (2). The ideality factor, n, is introduced to take the deviation of the experi-

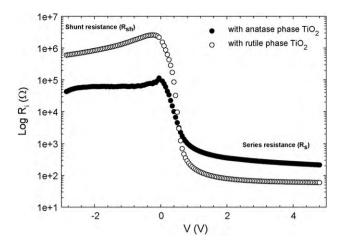

Fig. 2. The structure resistance of Au/n-Si structures with anatase and rutile phase  ${\rm TiO_2}.$

mental I-V data from the ideal TE theory into account. From Eq. (1), the value of n is calculated from the slope of the linear region of the forward bias  $\ln I-V$  plot and can be written as,

$$n = \frac{q}{kT} \left( \frac{dV}{d(\ln I)} \right) \tag{3}$$

The experimental values of  $\Phi_{\rm Bo}$  and n of Au/n-Si structures with anatase and rutile phase  ${\rm TiO_2}$  were calculated from Eq. (2) and Eq. (3) as 3.636 eV and 0.603 eV and 2.884 eV and 0.686 eV, respectively. There happens an increase in  $\Phi_{\rm Bo}$  and a decrease in the n as the annealing temperature increases. It is clear that the ideality factors of the structures are considerably larger than unity. These high values of n show that the device behaves as MIS structure rather than MS structure. The high values of n can be also attributed to existence of an insulator layer and wide distribution of low Schottky barrier height (SBH) patches at Au/n-Si interface, and particular distribution of  $N_{\rm SS}$  at Si/TiO<sub>2</sub> interface [27,30–32].

The series resistance  $(R_{\rm S})$  and shunt resistance  $(R_{\rm Sh})$  are determined from the structure resistance  $(R_{\rm i})$  versus applied bias voltage  $(V_{\rm i})$  plot determined from the I-V characteristics where  $R_{\rm i}=dV_{\rm i}/dI_{\rm i}$  and they were given in Fig. 2. It was observed that at sufficiently high forward bias voltage the structure's resistance values approach to a constant value such that the series resistance  $(R_{\rm S})$  values for Au/n-Si structures with anatase and rutile phase TiO<sub>2</sub> were found as 209  $\Omega$  and 59  $\Omega$ , respectively. Similarly, also at sufficiently high reverse bias voltage, the structure resistance values have a constant value, which is equal to structure's shunt resistance  $(R_{\rm Sh})$ , such that they are  $42~{\rm k}\Omega$  and  $598~{\rm k}\Omega$  for Au/n-Si structures with anatase and rutile phase TiO<sub>2</sub>, respectively.

There is a decrease in  $R_{\rm S}$  and an increase in  $R_{\rm Sh}$  with the increasing annealing temperature. Such behavior of  $R_{\rm S}$  and  $R_{\rm Sh}$  is a strong evidence of structural improvement with the increasing annealing temperature. In addition, the value of  $R_{\rm S}$  was calculated from the forward bias I-V data using the method of Cheung and Cheung [44]. From Eq. (1), the following functions can be rewritten as:

$$\frac{dV}{d(\ln I)} = n\left(\frac{kT}{q}\right) + IR_{\rm S} \tag{4a}$$

$$H(I) = V + n\frac{kT}{q}\ln\left(\frac{I}{AA^*T^2}\right) = n\Phi_{Bo} + IR_s$$

(4b)

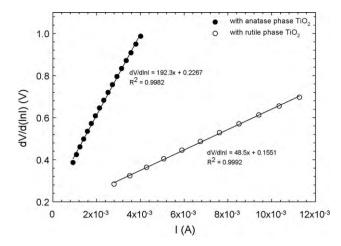

Here, in Eq. (4a) the term  $IR_{\rm S}$  is the voltage drop across the series resistance of the Au/TiO<sub>2</sub>/n-Si structures. The  $dV/d(\ln I) - I$  and H(I) - I plots of the structures were given in Figs. 3 and 4, respectively. In  $dV/d(\ln I) - I$  plot, the plot's slope gives the  $R_{\rm S}$  value, while the y-axis intercept gives the n value. According to Fig. 3, the  $R_{\rm S}$  and n values for Au/n-Si structures with anatase and rutile

**Fig. 3.** The  $dV/d(\ln I) - I$  characteristics of the Au/n-Si structures with anatase and rutile phase TiO<sub>2</sub> interfacial insulator layer.

phases  $\text{TiO}_2$  interfacial layer was found as 192.3  $\Omega$  and 48.5  $\Omega,$  and 8.9 and 6.1.

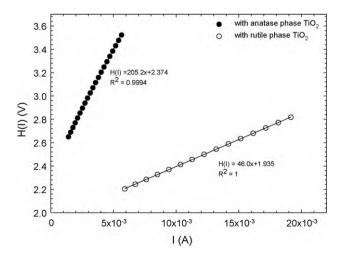

In H(I)-I graph given in Fig. 4, the plot's slope gives the  $R_{\rm S}$  value as the slope of  $dV/d(\ln I)-I$  plot. In addition, using the n value extracted from  $\ln I-V$  plot and the y-axis intercept, one can find the  $\Phi_{\rm Bo}$  value. According to Fig. 4, the  $R_{\rm S}$  and  $\Phi_{\rm Bo}$  values for Au/n-Si structures with anatase and rutile phase TiO<sub>2</sub> interfacial layer was found as 205.2  $\Omega$ , 46.0  $\Omega$  and 0.653 eV, 0.671 eV. The  $R_{\rm S}$  values obtained from  $dV/d(\ln I)-I$  and H(I)-I plots are in a good agreement with each other and the values obtained from  $\ln I-V$  graph.

To understand the current conduction mechanism in detail or to understand the deviation of  $\ln I - V$  plots from the linearity at the forward bias, the double logarithmic  $\log(I) - \log(V)$  plot can be used in addition to  $\ln I - V$  plot as given in Fig. 5.

According to the Fig. 5, both of plots have three distinct linear regions (region 1: -3V < V < -1.4V; region 2: -1 V < V < -0.6V; region 3: 0.2 V < V < 2V) that obey  $I\alpha V^m$  change. Here, m represents the slope of the each regions' linear section and was found as 1.60, 4.35 and 1.73 for Au/n-Si structure with anatase phase  $TiO_2$  and 1.89, 11.70 and 2.02 for Au/n-Si structure with rutile phase  $TiO_2$ , respectively. At low bias region (region 1), the current conduction mechanism for both of the samples exhibits an ohmic behavior, that is, the current is directly proportional to applied bias voltage [45]. This behavior can be attributed to the superiority of bulkgenerated current in the film to the injected free carrier generated

**Fig. 4.** The H(I) - I characteristics of the Au/n-Si structures with anatase and rutile phase  $TiO_2$  interfacial insulator layer.

**Fig. 5.** The  $\log(I) - \log(V)$  characteristics of the Au/n-Si structures with anatase and rutile phase  $TiO_2$  interfacial insulator layer.

current [45–47]. The second region for the both samples can be characterized by power law dependence. These behaviors obey the space-charge-limited-current (SCLC) theory that explains the increase in the injected electrons from the electrode to the films with the increasing applied voltage. The increase in the number of injected electrons causes filling up the traps and coming up the space charges [45–47]. At strong forward bias region (region 3), because of the strong electron injection, the electrons escape from the traps and contribute to space-charge-limited-current [45–49].

The non-linearity of  $\ln I - V$  characteristics at high bias values indicates a continuum of interface states in equilibrium with semiconductor [3]. Thus, the density distribution of the interface states  $N_{\rm ss}$  can be determined from the forward bias I - V characteristics. The effective barrier height  $\Phi_{\rm e}$  is given as:

$$\Phi_{\rm e} = \Phi_{\rm Bo} + \left(1 - \frac{1}{n(V)}\right)(V - IR_{\rm s}) \tag{5}$$

by considering the applied voltage dependency of  $\Phi_e$  due to the presence of an interfacial insulator layer (TiO<sub>2</sub>) and interface states located at the n-Si/TiO<sub>2</sub> interface. For Au/n-Si structures with anatase and rutile phase TiO<sub>2</sub> interfacial insulator layer density of interface states proposed by Card and Rhoderick can be simplified and given as [27]:

$$N_{\rm ss}(V) = \frac{1}{q} \left[ \frac{\varepsilon_{\rm i}}{\delta} (n(V) - 1) - \frac{\varepsilon_{\rm s}}{W_{\rm D}} \right] \tag{6}$$

where permittivity of semiconductor  $\varepsilon_s$  = 11.8 $\varepsilon_o$ , permittivity of insulator layer  $\varepsilon_i$  = 48 $\varepsilon_o$  for anatase phase and  $\varepsilon_i$  = 89 $\varepsilon_o$  for rutile phase TiO<sub>2</sub> [1] while  $\varepsilon_o$  (=8.85 × 10<sup>-14</sup> F/cm) is the permittivity of free space and  $W_D$  is the width of the space-charge region.

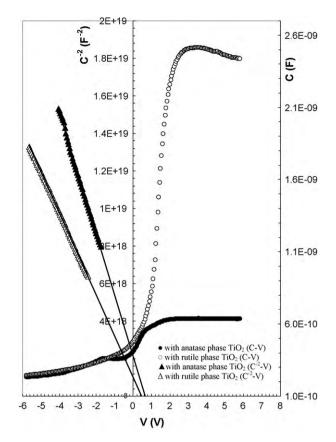

The capacitance-voltage (C-V) measurements were performed at 1 MHz frequency for the Au/n-Si structures with anatase and rutile phase TiO<sub>2</sub> interfacial insulator layer in order to find the interfacial insulator layer thickness  $\delta$  using the equation for insulator layer capacitance  $(C_{ox} = \varepsilon_i \varepsilon_o A/\delta)$  and the other electrical parameters such as built-in voltage  $V_i$ , Fermi energy  $E_F$ , donor concentration  $N_d$ and the width of the space-charge region  $W_D$ . At this sufficiently high frequency (1 MHz), the  $N_{\rm ss}$  cannot follow the ac signal and the contribution of interface states' capacitance to the total capacitance may be neglected. The thicknesses of the anatase and rutile phase TiO<sub>2</sub> interfacial insulator layers were calculated as 1516 Å, 2120 Å, respectively. The interfacial insulator layers thickness increased with increasing temperature due to the formation of SiO<sub>2</sub> insulator layer at the  $TiO_2/n$ -Si interface [26]. The C-V and  $C^{-2}-V$  characteristics of the structures were given in Fig. 6. As it can be seen from Fig. 6, the  $C^{-2}$ –V plot of the Au/n-Si structures with anatase and

**Fig. 6.** The C–V and C– $^2$ –V plots of Au/n-Si structures with anatase and rutile phase TiO $_2$  interfacial insulator layer.

rutile phase TiO<sub>2</sub> interfacial insulator layer give a straight line in wide range of bias voltage.

The depletion layer capacitance is given as [50].

$$C^{-2} = \frac{2(V_{\rm R} + V_{\rm i})}{q\varepsilon_{\rm s}N_{\rm d}A^2} \tag{7}$$

where  $V_R$  is the reverse bias voltage,  $N_d$  is the doping concentration and  $V_i$  is the built-in voltage at zero-bias, and it can be obtained by means of extrapolation of the  $C^{-2}-V$  plot to the voltage axis as  $0.667\,\mathrm{V}$  and  $0.500\,\mathrm{V}$  for the structures with anatase and rutile phases  $\mathrm{TiO}_2$  respectively. In addition, the doping concentration for the both structures was calculated as  $1.87\times10^{17}\,\mathrm{cm}^{-3}$ . Using the obtained  $V_i$  values the diffusion potential values at zero-bias were calculated using the following relation

$$V_{\rm d} = V_{\rm i} + \frac{kT}{q} \tag{8}$$

and they were found as  $0.692 \,\mathrm{V}$  and  $0.525 \,\mathrm{V}$  for the anatase and rutile phases  $\mathrm{TiO}_2$ , respectively. The depletion layer width  $W_\mathrm{D}$  values for both samples were also calculated from  $C^{-2} - V$  plots at 1 MHz frequency using the following equation [29]

$$W_{\rm D} = \sqrt{\frac{2\varepsilon_{\rm S}\varepsilon_{\rm o}V_{\rm d}}{qN_{\rm d}}}\tag{9}$$

and they were found as 140 Å and 122 Å for the Au/n-Si structures with anatase and rutile phases TiO<sub>2</sub>, respectively.

The Fermi energy level expression can be given as

$$E_{\rm F} = \frac{kT}{q} Ln \left( \frac{N_{\rm c}}{N_{\rm d}} \right) \tag{10}$$

where  $N_c$  is the effective density of states in the Si conductance band and given as  $2.86 \times 10^{19}$  cm<sup>-3</sup> [29]. The Fermi energy levels

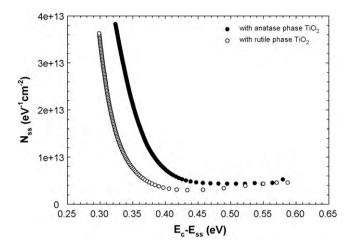

**Fig. 7.** Density of interface states as a function of  $E_c - E_{ss}$  of Au/n-Si structures with anatase and rutile phase TiO<sub>2</sub> interfacial insulator layer.

for both structures were calculated as 128 meV.

Thus, barrier height for the structures was obtained from C-V characteristics using the following relation neglecting the image force barrier lowering ( $\Delta \Phi_{\rm B}$ )

$$\Phi_{\rm B}(C-V) = V_{\rm d} + E_{\rm F} \tag{11}$$

and they were found as  $0.820\,\text{eV}$  and  $0.753\,\text{eV}$  for the Au/n-Si structures with anatase and rutile phases  $\text{TiO}_2$  respectively. These obtained values are in a good agreement with the barrier height values obtained from I-V characteristics and Cheung functions.

Furthermore, in n-type semiconductors, the energy of the interface states  $E_{ss}$  with respect to the bottom of the conduction band at the surface of semiconductor is given by:

$$E_{\rm c} - E_{\rm ss} = q(\Phi_{\rm e} - V) \tag{12}$$

The density of interface states  $N_{\rm SS}$ , as a function of  $E_{\rm c}-E_{\rm SS}$ , of Au/n-Si structures with anatase and rutile phase TiO<sub>2</sub> interfacial insulator layer was given in Fig. 7. As shown in Fig. 7, decrease in  $N_{\rm SS}$  from mid gap towards the bottom of conduction band with the increasing annealing temperature is very clear. The magnitude of the  $N_{\rm SS}$  of Au/n-Si structure with rutile phase TiO<sub>2</sub> is three times lower than that of anatase phase TiO<sub>2</sub>. This behavior was attributed to the molecular restructuring and reordering of Si and TiO<sub>2</sub> molecules at the metal–semiconductor interface [51], the particular distribution of  $N_{\rm SS}$  in the semiconductor band gap [52–54] and the better passivation property of rutile phase TiO<sub>2</sub> compared to anatase phase TiO<sub>2</sub> as a result of annealing temperature.

# 4. Conclusions

The main electrical parameters of Au/n-Si structures with anatase and rutile phase  $TiO_2$  interfacial insulator layer were investigated using I-V and C-V measurement methods at room temperature and compared with each other in terms of the effect of annealing temperature. The HRXRD patterns showed that the phase transition from amorphous phase to anatase and rutile phases occurs at  $700\,^{\circ}\text{C}$  and  $900\,^{\circ}\text{C}$ , respectively. Experimental results show that annealing temperature strongly affects the main electrical parameters, such as n,  $\Phi_B$ ,  $R_S$ ,  $R_{Sh}$  and  $N_{SS}$ . The rectifying ratio of Au/n-Si structure with rutile phase was found as 63 times higher than that of anatase phase  $TiO_2$ . Similarly, the leakage current of rutile phase was found to be 15 times lower than that of anatase phase. The energy distribution profile of  $N_{SS}$  at  $TiO_2/n$ -Si interface of the structures were extracted from the forward bias I-V data by taking the bias dependence of  $\Phi_e$  into account and the  $N_{SS}$  values

of both structures increase from the midgap towards the bottom of conduction band and decrease considerably with the increasing annealing temperature. In addition, the values of  $R_{\rm S}$  and  $R_{\rm Sh}$  were found to be as  $209\,\Omega$  and  $42\,{\rm k}\Omega$  for the anatase phase  ${\rm TiO_2}$  and  $59\,\Omega$  and  $59\,{\rm k}\Omega$  for the rutile phase  ${\rm TiO_2}$ . As a result, the Au/n-Si structures with rutile phase  ${\rm TiO_2}$  interfacial insulator layer showed better device performance and was found to be more suitable for this type of device fabrications.

# Acknowledgement

This work is supported by the State of Planning Organization of Turkey under Grant no. 2001K120590.

### References

- [1] W. Yang, J. Marino, A. Monson, C.A. Wolden, Semicond. Sci. Technol. 21 (12) (2006) 1573.

- [2] K.J. Han, K.S. Kang, Y. Chen, K.H. Yoo, J. Kim, J. Phys. D: Appl. Phys. 42 (12) (2009) 125110.

- [3] S.X. Zhang, D.C. Kundaliya, W. Yu, S. Dhar, S.Y. Young, L.G. Salamanca-Riba, S.B. Ogale, R.D. Vispute, T. Venkatesan, J. Appl. Phys. 102 (1) (2007) 013701.

- [4] W. Li, C. Ni, H. Lin, C.P. Huang, S.I. Shah, J. Appl. Phys. 96 (11) (2004) 6663.

- [5] N.R. Mathews, E.R. Morales, M.A. Cortes-Jacome, J.A.T. Antonio, Sol. Energy 83 (9) (2009) 1499.

- [6] O. Pakma, N. Serin, T. Serin, Ş. Altındal, J. Sol-Gel Sci. Technol. 50 (1) (2009) 28.

- [7] Z. Tekeli, Ş. Altındal, M. Çakmak, S. Özçelik, D. Çalışkan, E. Özbay, J. Appl. Phys. 102 (5) (2007) 054510.

- [8] H. Altuntas, A. Bengi, U. Aydemir, T. Asar, S.S. Cetin, I. Kars, S. Altindal, S. Ozcelik, Mater. Sci. Semicond. Proc. 12 (2009) 224.

- [9] O. Pakma, N. Serin, T. Serin, Ş. Altındal, J. Appl. Phys. 104 (1) (2008) 014501.

- [10] D.E. Yildiz, S. Altındal, H. Kanbur, J. Appl. Phys. 103 (12) (2008) 124502.

- [11] J.M.D. Coey, Solid State Sci. 7 (6) (2005) 660.

- [12] H.Y. Guo, Z.G. Ye, Mater. Sci. Eng. B-Solid 120 (1-3) (2005) 68.

- [13] L. Truong, Y.G. Fedorenko, V.V. Afanasev, A. Stesmans, Microelectron. Reliab. 45 (5–6) (2005) 823.

- [14] Y.X. Leng, N. Huang, P. Yang, J.Y. Chen, H. Sun, J. Wang, G.J. Wan, Y. Leng, P.K. Chu, Thin Solid Films 420–421 (2002) 408.

- [15] K.M. Reddy, S.V. Manorama, A.R. Reddy, Mater. Chem. Phys. 78 (1) (2002) 239.

- [16] S. Banerjee, J. Gopal, P. Muraleedharan, A.K. Tyagi, B. Raj, Curr. Sci. India 90 (10) (2006) 1378.

- [17] B.H. Lee, Y. Jeon, K. Zawadzki, W.J. Qi, J. Lee, Appl. Phys. Lett. 74 (21) (1999) 3143.

- [18] K.S. Yeung, Y.W. Lam, Thin Solid Films 109 (2) (1983) 169.

- [19] M. Lottiaux, C. Boulesteix, G. Nihoul, F. Varnier, F. Flory, R. Galindo, E. Pelletier, Thin Solid Films 170 (1) (1989) 107.

- [20] M.R. Kozlowski, P.S. Tyler, W.H. Smyrl, R.T. Atanasoki, J. Electrochem. Soc. 136 (2) (1989) 442.

- [21] K.A. Vorotilov, E.V. Orlova, V.I. Petrovsky, Thin Solid Films 207 (1–2) (1992) 180.

- [22] M. Gartner, C. Parlog, P. Osiceanu, Thin Solid Films 234 (1–2) (1993) 561.

- [23] L.M. Williams, D.W. Hess, J. Vac. Sci. Technol. A 1 (4) (1983) 1810.

- [24] L.J. Meng, M. Andritschky, M.P. dos Santos, Thin Solid Films 223 (2) (1993) 242.

- [25] H. Tang, K. Prasad, R. Sanjines, P.E. Schmid, F. Levy, J. Appl. Phys. 75 (4) (1994) 2042.

- [26] M. Kadoshima, M. Hiratani, Y. Shimamoto, K. Torii, H. Miki, S. Kimura, T. Nabatame, Thin Solid Films 424 (2) (2003) 224.

- [27] H.C. Card, E.H. Rhoderick, J. Phys. D-Appl. Phys. 4 (10) (1971) 1589.

- [28] E.H. Rhoderick, R.H. Williams, Metal-Semiconductor Contacts, second ed., Oxford, 1978.

- [29] S.M. Sze, Physics of Semiconductor Devices, second ed., John Wiley & Sons Inc., New York, 1981.

- [30] Ş. Karataş, Ş. Altındal, A. Türüt, A. Özmen, Appl. Surf. Sci. 217 (1–4) (2003) 250.

- [31] M.K. Hudait, S.B. Krupanidhi, Mater. Sci. Eng. B-Solid 87 (2) (2001) 141.

- [32] J.H. Werner, H.H. Güttler, J. Appl. Phys. 69 (3) (1991) 1522.

- [33] A.S. Kavasoğlu, F. Yakuphanoğlu, N. Kavasoğlu, O. Pakma, O. Birgi, S. Oktik, J. Alloys Compd. 492 (2010) 421.

- [34] M. Sağlam, A. Ateş, B. Güzeldir, A. Astam, M.A. Yıldırım, J. Alloys Compd. 484 (2009) 570.

- [35] V. Baranwal, S. Kumar, A.C. Pandey, D. Kanjilal, J. Alloys Compd. 480 (2009) 962.

- [36] H. Xue, X. Guan, R. Yu, Z. Xiong, J. Alloys Compd. 482 (2009) L14.

- [37] A. Tataroğlu, Ş. Altındal, J. Alloys Compd. 479 (2009) 893.

- [38] P. Chattopadhyay, A.N. Daw, Solid State Electron. 29 (5) (1986) 555.

- 39] A. Chawanda, C. Nyamhere, F.D. Auret, W. Mtangi, M. Diale, J.M. Nel, J. Alloys Compd. 492 (2010) 649.

- [40] F. Yakuphanoğlu, J. Alloys Compd. 494 (2010) 451.

- [41] A. Tataroğlu, Ş. Altındal, J. Alloys Compd. 484 (2009) 405.

- [42] L.S. Chuah, Z. Hassan, H. Abu Hassan, N.M. Ahmed, J. Alloys Compd. 481 (2009)

- [43] F. Kang, J. Ao, G. Sun, Q. He, Y. Sun, J. Alloys Compd. 478 (2009) L25.

- [44] S.K. Cheung, N.W. Cheung, Appl. Phys. Lett. 49 (2) (1986) 85.

- [45] S. Wagle, V. Shirodkar, Braz. J. Phys. 30 (2) (2000) 380.

- [46] Y.S. Ocak, M. Kulakci, T. Kılıcoglu, R. Turan, K. Akkılıc, Synth. Met. 159 (15–16) (2009) 1603.

- [47] Ř. Şahingöz, H. Kanbur, M. Voigt, C. Soykan, Synth. Met. 158 (17–18) (2008) 727.

- [48] H. Wang, X.N. Shen, X.J. Su, Z. Wang, S.X. Shang, M. Wang, Ferroelectrics 195 (1) (1997) 233.

- [49] Ö. Güllü, S. Aydoğan, A. Türüt, Microelectron. Eng. 85 (7) (2008) 1647.

- [50] M.K. Hudait, S.B. Krupanidhi, Solid State Electron. 44 (6) (2000) 1089.

- [51] B. Akkal, Z. Benemara, A. Boudissa, N.B. Bouiadjra, M. Amrani, L. Bideux, B. Gruzza, Mater. Sci. Eng. B-Solid 55 (3) (1998) 162.

- [52] E.H. Rhoderick, J. Appl. Phys. 46 (6) (1975) 2809.

- [53] I. Dokme, S. Altındal, Semicond. Sci. Technol. 21 (8) (2006) 1053.

- [54] S. Karatas, S. Altındal, M. Cakar, Physica B 357 (3-4) (2005) 386.